# Surface treatments to reduce leakage current in In<sub>0.53</sub>Ga<sub>0.47</sub>As p-i-n diodes

Abhinav Gaur, al Ian Manwaring, Matthew J. Filmer, Paul M. Thomas, and Sean L. Rommel Department of Electrical and Microelectronic Engineering, Rochester Institute of Technology, Rochester, New York 14623

# Kunal Bhatnagar and Ravi Droopad

Ingram School of Engineering, Texas State University, San Marcos, Texas 78666

(Received 7 November 2014; accepted 17 February 2015; published 18 March 2015)

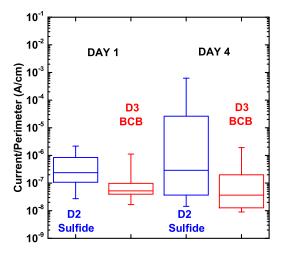

The impact of mesa surface conditions on the dark current of a homojunction In<sub>0.53</sub>Ga<sub>0.47</sub> As p-i-n diode has been investigated. Three treatments were performed on mesa structures with a 100 nm i-layer—sidewall exposure to O<sub>2</sub> plasma, sulfide treatment, and divinylsiloxane-bis-benzocyclobutene (BCB) passivation that resulted in perimeter normalized current,  $J_1$ , of 0.01 A/cm, 0.35  $\mu$ A/cm, and 35 nA/cm, respectively. This study spanned several days and it was shown that sulfide layer, unless properly capped, deteriorates over time whereas the BCB passivation properly encapsulates the mesa and does not degrade for longer periods of time. © 2015 American Vacuum Society. [http://dx.doi.org/10.1116/1.4914403]

### I. INTRODUCTION

With the advancement of the low-power electronics industry in the past decade, there is a drive to reduce power consumption to increase battery life while maintaining high performance. Constant field scaling necessitates  $V_{\rm dd}$  scaling with every generation. As CMOS devices are being scaled down, there has come a time when dynamic power and static power dissipation of an individual device are comparable, because of thermionic emission, which is the dominant carrier transport mechanism in a MOS-FET. In a tunnel fieldeffect transistor (TFET), instead of hopping over a barrier, the carriers are transported through a mechanism of quantum mechanical band-to-band tunneling, which does not limit the subthreshold swing to 60 mV/decade as in the case of a MOSFET. Because the swing can be sub-60 mV/decade,<sup>2</sup> the off-current can be significantly reduced, while maintaining a high on-state current. High drive currents have been demonstrated by bandgap engineering in heterojunction TFETs (Refs. 3 and 4) and  $\delta$ -doping in homojunction structures, 5,6 but they still lag behind MOS-FETs at the equivalent technology node. This paper addresses the problem of off-state current in a homojunction In<sub>0.53</sub>Ga<sub>0.47</sub>As TFET.

A TFET operates as a reverse-biased p-i-n diode with a gate over the intrinsic region. The off-state current of a TFET can therefore be defined as the current flowing in a pi-n diode in reverse bias mode, or leakage current. In vertical mesa p-i-n structures, leakage current can be either bulk leakage (area-dominated) or surface leakage (perimeterdominated). A lot of photodetector literature has focused on bulk leakage as the major contributor to leakage in a p-i-n diode, but as the dimensions of a device are being scaled down, the surface impact on leakage increases tremendously. It has been shown that an in an unpassivated device with an In or Ga rich surface, the mesa sidewall oxidizes when exposed to atmosphere, leading to Fermi level pinning at the surface. The inversion layer has an ohmic contact to the ntype substrate and forms a sidewall p-n junction at the p<sup>++</sup>/i

This study shows the effectiveness of two surface treatments—a sulfide treatment and divinylsiloxane-bis-benzocyclobutene (BCB) passivation—in reducing leakage current in a homojunction In<sub>0.53</sub>Ga<sub>0.47</sub>As p-i-n diode. Sulfur in ammonium sulfide, (NH<sub>4</sub>)<sub>2</sub>S, is known to passivate dangling bonds at III–V surfaces. 12,13 BCB is a polymer resin that has been traditionally used in the industry as a planarizing material and a low-k inter-layer dielectric.

# II. EXPERIMENT

In this study, a homojunction In<sub>0.53</sub>Ga<sub>0.47</sub>As p-i-n structure was grown using molecular beam epitaxy on an InP substrate. The layer structure consisted of a 30 nm p<sup>++</sup> doped region followed by a 100 nm intrinsic region. A 30 nm n<sup>++</sup> region was grown on top of the intrinsic region (Fig. 1a). For a comparative study spanning multiple days of electrical testing, four samples of the p-i-n structure were used.

Two hundred nanometer of Mo was deposited by DC sputtering. The mesa patterns were defined by optical lithography using a g-line stepper. The pattern was transferred to the Mo in a RIE chamber using SF<sub>6</sub> chemistry. Using the etched Mo as a hard mask, the In<sub>0.53</sub>Ga<sub>0.47</sub>As mesa etch was performed using a 20:1 citric acid:H<sub>2</sub>O<sub>2</sub> solution<sup>14</sup> for 118 s. The control sample, D1, was tested directly after the etch. Sample D2 was dipped in a 1:4 (NH<sub>4</sub>)<sub>2</sub>S:H<sub>2</sub>O solution for 10 min post the mesa etch, followed by a quick rinse in isopropyl alcohol and water after which it was immediately tested. D3 was coated with Cyclotene 3022-35 (1:1 BCB:Mesitylene) after the citric etch followed by a 5 min bake at 140 °C and curing at 250 °C in a N2 ambient for 60 min. After the cure, BCB was etched back to expose the

interface. Tunneling occurs when the p-side is heavily doped and the energy of electrons in the p++ region overlaps the empty states in the conduction band of the n<sup>++</sup> region causing a shunt path for current to flow without the application of any gate bias.<sup>8–10</sup> Low temperature characterization done by Lin<sup>11</sup> showed the impact of surface leakage on the reverse-bias current in a p-i-n diode, by depleting the surface of charge carriers.

a) Electronic mail: axg4430@rit.edu

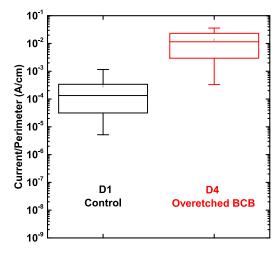

top metal, which was done in a plasma etch tool using a combination of  $O_2$  and  $SF_6$  based chemistry. After the desired thickness of BCB was etched, D3 was tested. In the fourth sample, D4, BCB was further etched to expose the mesa sidewall to an  $O_2$  plasma after which it was tested. The basis of the overetch was that surface oxidation leads to parallel conduction paths in a III–V diode and to therefore study the impact of oxidation, an extreme case of exposure to an  $O_2$  plasma was implemented (Fig. 1).

## **III. RESULTS AND DISCUSSION**

In order to standardize leakage current for a proper comparison of treatments across diodes of different sizes,  $I_0$ observed at a reverse bias of 0.5 V was normalized with perimeter of the cross-section of the device, referred to as  $J_1$  (A/cm). The layout of devices on the mask set was such that devices of 40 different perimeters were tested. Measurements were taken immediately after performing the particular treatment (day 1) and then on day 4 and day 8. Box charts have been used for comparisons of different treatments that represent the median of the data (the midline in the box) and the top and bottom edges of the box, or the interquartile range (IQR) represents the middle 50% of the data. The lines extending from the box represent the maximum and minimum of the dataset. It is widely accepted that the IQR is a better tool to analyze the distribution of the data than the maximum-minimum range.

Surface traps and dangling bonds can occupy a discrete level or a band of trap states in the energy gap. If it traps a high number of carriers, then the Fermi level at the surface

| 30 nm     | In <sub>0.53</sub> Ga <sub>0.47</sub> As | n**  |

|-----------|------------------------------------------|------|

| 100 nm    | In <sub>0.53</sub> Ga <sub>0.47</sub> As | i    |

| 30 nm     | In <sub>0.53</sub> Ga <sub>0.47</sub> As | p++  |

| Substrate | InP                                      | S.I. |

(a)

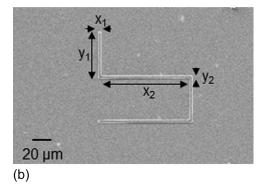

Fig. 1. (a) Layer structure of the samples and (b) top-down scanning electron micrograph of a typical high-perimeter serpentine pattern. The pattern is the metal on top of the mesa, with the cross-sectional area defined as  $\mathbf{n}^*(x_1y_1+x_2y_2)$  and the perimeter defined as  $\mathbf{n}^*(2(x_1+y_1+x_2+y_2))$ , where n is the number of repetitions of the L-shaped pattern.

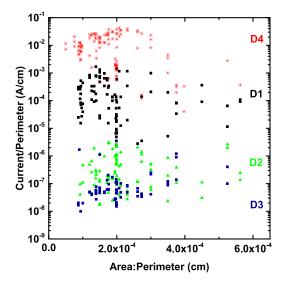

Fig. 2. (Color online) Scatter plot of  $J_1$  (A/cm) vs ratio of area to perimeter (cm) of the cross-section of the device comparing leakage current post BCB passivation (D3, blue), sulfide passivation (D2, green), and sidewall oxidation (D4, red) from the control sample (D1, black).

becomes insensitive to gate modulation as there would always be an inversion layer present at the interface. Without the application of gate bias,  $^{11}$  there would be a possibility of charge carriers tunneling across the barrier at the  $p^{++}/i$  interface, causing a substantial increase in the off-state current. This has also been observed in experimental demonstration of III–V MOSFETs.  $^{15-17}$  In this study, Fig. 2 suggests that there may be a correlation of formation of  $In_xO_y$  and  $Ga_xO_y$  at the surface and increase in  $I_0$  in the samples, particularly, D1 and D4. However, an XPS would be required to corroborate the claim.

# A. Ammonium sulfide passivation

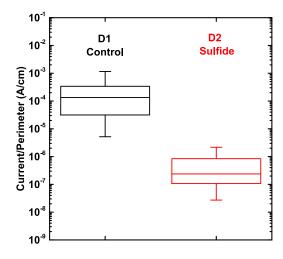

Figure 2 shows a scatter plot of surface leakage current,  $J_1$  (A/cm) that compares  $I_0$  in the sulfide sample (D2) to the control sample (D1). In the graph,  $J_1$  has been plotted against the ratio of area to perimeter of the cross-section of the device to compare surface leakage in the two samples. A statistical comparison is shown in Table I.  $J_1$  in the control sample spanned from  $3 \times 10^{-6}$  to  $2 \times 10^{-3}$  A/cm without a definite trend. In D2, the scatter points remained random but scaled down two to three orders of magnitude  $-1 \times 10^{-8}$  to  $4 \times 10^{-6}$  A/cm with the median at 2.37  $\times 10^{-7}$  A/cm (Fig. 3).

Table I. Surface treatment and its impact on median perimeter normalized current,  $J_1$  (A/cm).

| Sample | Treatment                                    | No. of samples tested | J <sub>1</sub> day 1 (A/cm) | J <sub>1</sub> day 4 (A/cm) |

|--------|----------------------------------------------|-----------------------|-----------------------------|-----------------------------|

| DI     | Control sample                               | 97                    | $3.5 \times 10^{-6}$        | $1.3 \times 10^{-4}$        |

| D2     | Sulfide passivation                          | 84                    | $2.37 \times 10^{-7}$       | $3.5 \times 10^{-7}$        |

| D3     | BCB passivation                              | 74                    | $5.2 \times 10^{-8}$        | $3.5 \times 10^{-8}$        |

| D4     | Sidewall exposed<br>to O <sub>2</sub> plasma | 107                   | $1.15 \times 10^{-2}$       | _                           |

Fig. 3. (Color online) Comparison of  $J_1$  (A/cm) in control sample, D1, with a sample treated with ammonium sulfide passivation, D2. Current drops roughly 2.5 orders of magnitude in D2.

### **B. BCB passivation**

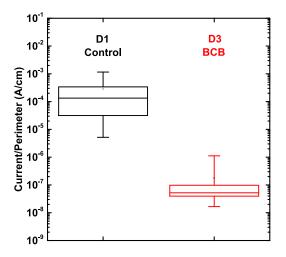

In the box plot of the BCB passivation in Fig. 4, the effectiveness of the passivation is shown by the dark current dropping 4 orders of magnitude—from  $1.3 \times 10^{-4}$  A/cm in the control sample to  $3.5 \times 10^{-8}$  A/cm in the sample passivated with BCB, D4. Qualitatively, it was observed that as the area begins to dominate the perimeter, the effectiveness of the clean was not that evident in D4 and  $I_0$  was much closer to D1, suggesting bulk current domination, which would be similar in both devices. This suggests that BCB is successful is passivating the dangling bonds at the  $I_{0.53}Ga_{0.47}As$  surface and is successful in mesa encapsulation and preventing  $O_2$  from oxidizing the surface.

From day 1 to day 4,  $J_1$  in D1 increased from  $3.5 \times 10^{-6}$  to  $1.3 \times 10^{-4}$  A/cm, indicating sidewall surface oxidation resulting in the formation of conductive  $In_xO_y$  and  $Ga_xO_y$ . The current spread was confined from 4 orders of magnitude on day 1 to one order spread on day 4. It was observed that the lower IQR has shifted by more than three orders from

Fig. 4. (Color online) Comparison of  $J_1$  (A/cm) in the control sample, D1, with the sample treated with BCB, D3. Current drops 3.5 orders of magnitude in D3.

day 1 to day 4. All the devices in D1 performed worse on day 4 than on day 1.

When compared with the BCB and the sulfide samples, in Fig. 5, it was observed that in D3, the variation in data increased from day 1 to day 4 but  $I_0$  dropped marginally. This is because on and around devices with a large crosssectional area, BCB etches faster than on smaller devices, leading to a possible overetch that exposes the mesa to the atmosphere that results in a higher leakage. In contrast, devices with a small area on which the BCB has not been overetched demonstrate a similar leakage as on day 1, asserting that it provides complete mesa encapsulation from the environment. In contrast, the spread of  $I_0$  in the sulfide sample increased from one order of magnitude (on day 1) to four orders on day 4 and day 8. This could be attributed to the fact that sulfur passivation deteriorates over time. The sulfur atoms that tie up the dangling bonds at the mesa sidewall either diffuse out into the atmosphere creating dangling bonds or are replaced by oxygen atoms that react with the In and Ga atoms to form conductive oxides. Devices that have larger perimeters have a higher probability of sulfur escaping into the atmosphere. The serpentine patterns (Fig. 1b) in the mask were of a very high perimeter to area ratio, which could be responsible for an increase in the spread. However, as the area to perimeter ratio increased (moving toward a square mesa), current levels on day 4 were similar to those on day 1—hence, the median remained constant. The BCB consistently shows lower  $I_0$  than sulfide over the complete range of varying area and perimeter devices, both on day 1 and day 4. Day 8 data say a similar story as the measurements were similar to day 4 results and have been omitted from the figures.

#### C. BCB overetch

The surface oxidation process due to exposure to ambient environment was accelerated by exposing the mesa sidewall to an  $O_2$  plasma. This was done to see the extent of increase in  $J_1$  caused by surface damage and oxidation. In D4,  $J_1$  was

Fig. 5. (Color online) Comparison of two passivation treatments—sulfide (blue) and BCB (red) on day 1 and day 4 to see change in leakage current in D2 and D3 p-i-n devices.

Fig. 6. (Color online) Effect of  $O_2$  plasma on mesa sidewall in a BCB etchback (red) process. Surface leakage increased by 2 orders of magnitude in D4.

observed to be two orders of magnitude higher than D1 consistently across devices of high perimeter to area ratios, evident from Fig. 2. The surface oxidation is responsible for the degradation in  $J_1$ . The exposure of the sidewall to the  $O_2$  plasma rapidly oxidized the semiconductor to form conductive  $In_xO_y$  and  $Ga_xO_y$ . Devices that had a large area and relatively small perimeters (high area to perimeter ratios) showed little or no difference in leakage between the two samples reinforcing the fact that surface oxidation is responsible for increasing leakage current (Fig. 6).

## IV. CONCLUSION

Different treatment combinations to reduce  $I_0$  in a homojunction  $In_{0.53}Ga_{0.47}As$  p-i-n diode have been studied. At a reverse bias of V=0.5 V and room temperature, the off-state current of the control, sulfide and BCB sample are  $1.3 \times 10^{-4}$ ,  $3.5 \times 10^{-7}$ , and  $3.5 \times 10^{-8}$  A/cm, respectively. In addition, a p-i-n structure exposed to an  $O_2$  plasma showed an increase in leakage by almost two orders of magnitude to 0.01 A/cm.

BCB passivation showed consistent improvement over sulfide treatment in reducing  $I_0$  across devices of varying dimensions. Whereas sulfide treatment showed degradation over time, the BCB passivation successfully isolated the mesa side-wall from deterioration by the ambient.

#### **ACKNOWLEDGMENTS**

The authors acknowledge financial support from SE-MATECH, National Science Foundation Grant No. ECCS-1202054, and the RIT Office of the Vice President for Research as well as technical support from J. Nash, B. Tolleson, S. O'Brien, and D. Yackoff of the RIT Semiconductor & Microsystems Fabrication Laboratory.

<sup>1</sup>R. H. Dennard, F. H. Gaensslen, H. Yu, V. L. Rideout, E. Bassous, and A. R. Leblanc, Proc. IEEE 87, 668 (1999).

<sup>&</sup>lt;sup>2</sup>A. C. Seabaugh and Q. Zhang, Proc. IEEE **98**, 2095 (2010).

<sup>&</sup>lt;sup>3</sup>R. Bijesh *et al.*, IEEE Int. Electron Devices Meet. **2013**, 28.2.1.

<sup>&</sup>lt;sup>4</sup>G. Dewey *et al.*, IEEE Int. Electron Devices Meet. **2011**, 33.6.1.

<sup>&</sup>lt;sup>5</sup>H. Zhao, Y. Chen, Y. Wang, F. Zhou, F. Xue, and J. C. Lee, Appl. Phys. Lett. **98**, 93501 (2011).

<sup>&</sup>lt;sup>6</sup>D. Mohata et al., Appl. Phys. Express 4, 024105 (2011).

<sup>&</sup>lt;sup>7</sup>H. Zhao, Y. Chen, Y. Wang, F. Zhou, F. Xue, and J. Lee, IEEE Trans. Electron Dev. **58**, 2990 (2011).

<sup>&</sup>lt;sup>8</sup>S. Maniv, Proc. SPIE. **0819**, 103 (1987).

<sup>&</sup>lt;sup>9</sup>I. Bloom and Y. Nemirovsky, IEEE Trans. Electron Devices **40**, 309(1993).

<sup>&</sup>lt;sup>10</sup>L. Ray-Ming, T. Shiang-Feng, and C. H. Kuan, J. Vac. Sci. Technol. B 18, 2624 (2000).

<sup>&</sup>lt;sup>11</sup>R. Lin, S. Tang, S. Lee, C. Kuan, G. Chen, T. Sun, and J. Wu, IEEE Trans. Electron Devices 44, 209 (1997).

<sup>&</sup>lt;sup>12</sup>V. N. Bessolov, Y. Zhilyaev, E. V. Konenkova, and M. V. Lebe-dev, Tech. Phys. 43, 983 (1998).

<sup>&</sup>lt;sup>13</sup>Y. Xuan, Y. Q. Wu, T. Shen, T. Yang, and P. D. Ye, IEEE Int. Electron Devices Meet. 2007, 637.

<sup>&</sup>lt;sup>14</sup>G. C. DeSalvo, W. F. Tseng, and J. Comas, J. Electrochem. Soc. **139**, 831

<sup>&</sup>lt;sup>15</sup>W. Chen, X. Min, G. Jiangjiang, D. W. Zhang, and P. D. Ye, Electrochem. Solid State Lett. 15, H51 (2012).

<sup>&</sup>lt;sup>16</sup>R. Engel-Herbert, H. Yoontae, and S. Stemmer, Appl. Phys. Lett. 97, 62905 (2010).

<sup>&</sup>lt;sup>17</sup>A. Ali et al., 68th Annual Device Research Conference (IEEE, Piscataway, NJ, 2010), p. 27.

Copyright of Journal of Vacuum Science & Technology: Part B-Nanotechnology & Microelectronics is the property of AVS, The Science & Technology Society and its content may not be copied or emailed to multiple sites or posted to a listserv without the copyright holder's express written permission. However, users may print, download, or email articles for individual use.