# CAPACITY MODEL WITH SUSTAINABILITY SCOPE TO PREDICT THE SEMICONDUCTOR MANUFACTURING'S ENERGY CONSUMPTION AND CARBON DIOXIDE EMISSIONS

by

Thulasi Krishna Kannaian B.S.

A thesis submitted to the Graduate Council of Texas State University in partial fulfillment of the requirements for the degree of Master of Science with a Major in Engineering December 2018

## Committee Members:

Jesus A. Jimenez, Chair

Cecilia Temponi, Co-Chair

Tongdan Jin

# **COPYRIGHT**

by

Thulasi Krishna Kannaian

2018

## FAIR USE AND AUTHOR'S PERMISSION STATEMENT

#### Fair Use

This work is protected by the Copyright Laws of the United States (Public Law 94-553, section 107). Consistent with fair use as defined in the Copyright Laws, brief quotations from this material are allowed with proper acknowledgment. Use of this material for financial gain without the author's express written permission is not allowed.

# **Duplication Permission**

As the copyright holder of this work I, Thulasi Krishna Kannaian, authorize duplication of this work, in whole or in part, for educational or scholarly purposes only.

# **DEDICATION**

I would like to dedicate this thesis to my family for all the guidance, encouragement and support throughout my life. I also dedicate this report to my friends for their constant help and support.

#### **ACKNOWLEDGEMENTS**

I would like to express my gratitude to all who helped me during the wring of this thesis at Texas State University.

First, I would like to express my deep gratitude to Dr. Jesus A. Jimenez, my Supervisor, for his continuous support and encouragement, for his patience, motivation, enthusiasm, and immense knowledge. He also provides me with an excellent atmosphere for conducting this research project. Without his consistent and illuminating instruction, this thesis could not have reached its present form.

I would also like to express my heartfelt gratitude to my thesis committee members: Dr. Cecilia Temponi and Dr. Tongdan Jin for their insightful comments and constructive suggestions in the early version of the work.

I owe a special debt of gratitude to Dr. Vishu Viswanthan, Graduate Advisor of Engineering, and Dr. Stan McClellan, former Director of Ingram School of Engineering, for providing facility support. I would also like to thank Dr. Patrick L. Thomas and Ms. Sarah Pierce in Ingram School of Engineering for their kind help.

Finally, I express my gratitude to my parents, family and friends for providing me with unfailing support and continuous encouragement throughout my years of study and through the process of researching and writing this thesis. This accomplishment would not have been possible without them.

# TABLE OF CONTENTS

| Page                                                    |

|---------------------------------------------------------|

| ACKNOWLEDGEMENTSv                                       |

| LIST OF TABLESix                                        |

| LIST OF FIGURESx                                        |

| LIST OF ABBREVATIONSxi                                  |

| ABSTRACTxiii                                            |

| CHAPTER                                                 |

| 1. INTRODUCTION1                                        |

| 1.1 Problem Description                                 |

| 1.2 Research Objective                                  |

| 1.3 Thesis Outline5                                     |

| 2. LITERATURE REVIEW6                                   |

| 2.1 Semiconductor Manufacturing6                        |

| 2.2 Electricity Consumption                             |

| 2.3 Factors Affecting Energy Consumption in Wafer Fab   |

| 2.4 Simulation Models with Renewable Energy Integration |

| 2.5 Carbon Emission and Carbon Tax                      |

| 2.6 Production Planning of the Supply Chain Model21     |

| 2.7 Modeling Sustainability for Production Planning24   |

| 3. | METHODOLOGY                                                                                           | .30  |

|----|-------------------------------------------------------------------------------------------------------|------|

|    | 3.1 List of Variables and Parameters                                                                  | .31  |

|    | 3.2 Capacity Performance Measures                                                                     | . 32 |

|    | 3.3 Electricity Consumption Metrics                                                                   | .33  |

|    | 3.4 Comparison of PEI and EUI                                                                         | . 34 |

|    | 3.5 Capacity Model for Electrical Power Consumption Estimation usin WIP Lot Data (kWh-WIP)            |      |

|    | 3.6 Capacity Model for Electrical Power Consumption Estimation usin Tool-level Utilization (kWh-Tool) |      |

|    | 3.7 Carbon Dioxide Emission Calculation                                                               | . 38 |

|    | 3.8 Description of Simulation Model                                                                   | . 38 |

|    | 3.9 Selection of Optimal PEI value                                                                    | . 43 |

|    | 3.10 Simulation Process                                                                               | . 43 |

| 4. | RESULTS AND DISCUSSION                                                                                | . 47 |

|    | 4.1 Design of Experiments                                                                             | . 47 |

|    | 4.2 Design of Simulation Experiment                                                                   | . 49 |

|    | 4.3 Results for the kWh-WIP                                                                           | . 50 |

|    | 4.4 Results for the kWh-Tool                                                                          | . 54 |

|    | 4.5 Comparisons between kWh-WIP vs. kWh-Tool                                                          | . 55 |

|    | 4.6 Error %                                                                                           | . 58 |

|    | 4.7 Insights of kWh-WIP                                                                               | . 59 |

|    | 4.8 Insights of kWh-Tool                                                                              | 59   |

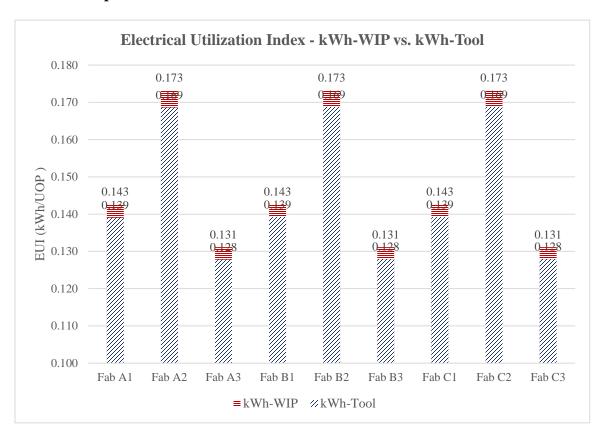

|    | 4.9 EUI Comparison                        | . 60 |

|----|-------------------------------------------|------|

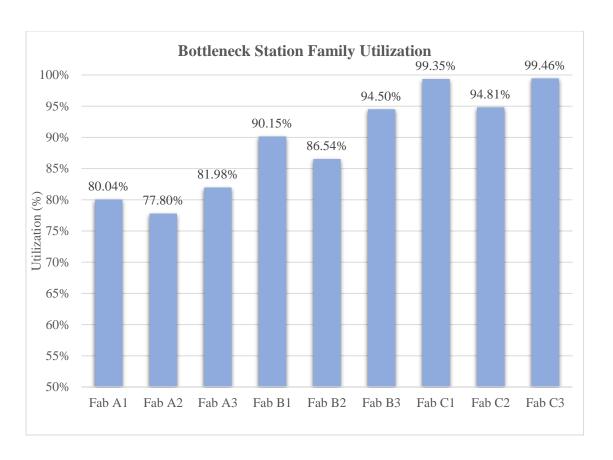

|    | 4.10 Bottleneck Station Utilization Study | . 61 |

|    | 4.11 CO <sub>2</sub> Emission Calculation | . 63 |

| 5. | CONCLUSION AND FUTURE WORK                | . 66 |

|    | 5.1 Conclusion                            | . 66 |

|    | 5.2 Managerial Decision Making and Impact | . 67 |

|    | 5.2 Future Work                           | . 68 |

| A  | PPENDIX SECTION                           | . 70 |

| p  | FEFRENCES                                 | 88   |

# LIST OF TABLES

| Table |                                                                         | Page |

|-------|-------------------------------------------------------------------------|------|

| 1     | . Station Family –Process Mapping                                       | 40   |

| 2     | . Wafer Fab Production and Energy Indices                               | .43  |

| 3     | . Fab Profile Definition                                                | 48   |

| 4     | . Repeats Calculation for Each Scenario or Fab Type                     | 49   |

| 5     | Power Consumption Calculation for the kWh-WIP method                    | .52  |

| 6     | PEI Analysis for the kWh-WIP method                                     | .53  |

| 7     | EUI Analysis for the kWh-WIP method                                     | .53  |

| 8     | Fab Profile Comparison                                                  | .56  |

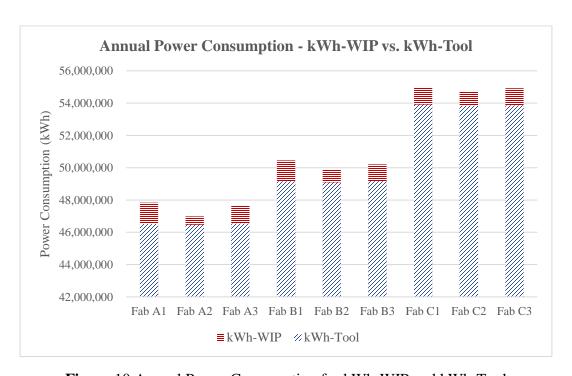

| 9     | . Annual Power Consumption values for kWh-WIP and kWh-Tool              | .57  |

| 1     | 0. Annual Power Consumption Error% between kWh-WIP and kWh-Tool         | .58  |

| 1     | Bottleneck Station-Process and Utilization percentage for each fab type | 61   |

| 1     | 2. Carbon Dioxide Calculation for Fabs based on kWh-WIP                 | 64   |

# LIST OF FIGURES

| Figure |                                                                       | Page |

|--------|-----------------------------------------------------------------------|------|

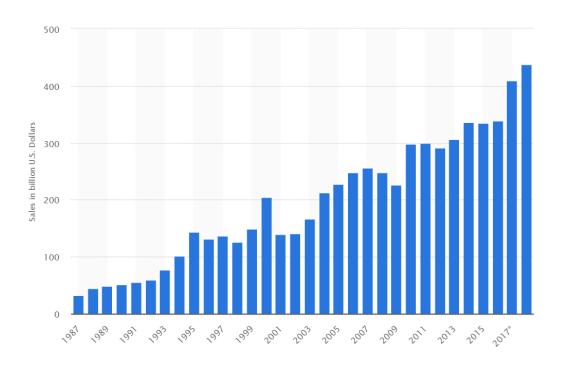

| 1.     | Global Semiconductor Sales from 1987 to 2017                          | 1    |

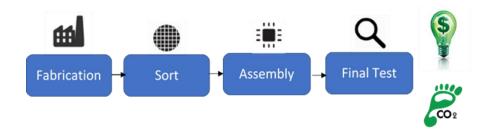

| 2.     | Semiconductor Manufacturing                                           | 6    |

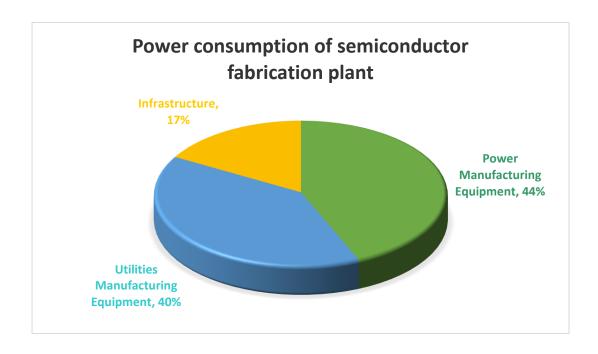

| 3.     | Power Consumption of Semiconductor Fabrication Plant                  | 9    |

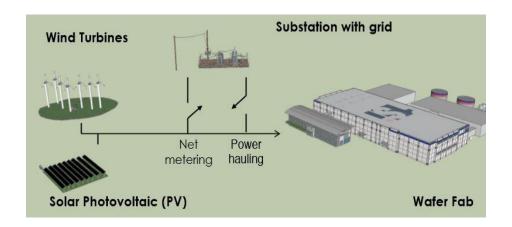

| 4.     | A Grid-Connected Solar PV System and Wind Turbine System              | . 15 |

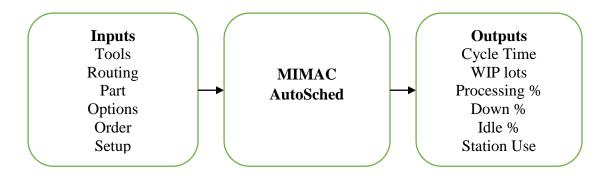

| 5.     | Inputs and Outputs for the MIMAC Model                                | . 39 |

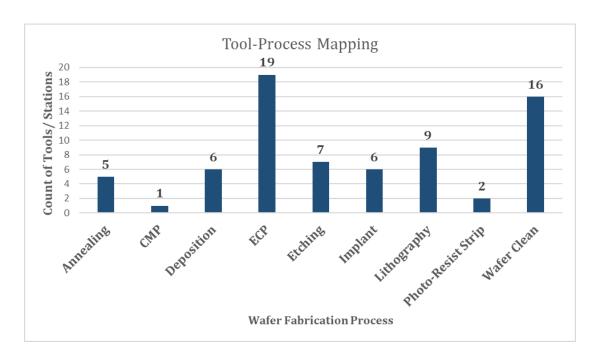

| 6.     | Number of tools in each process                                       | .41  |

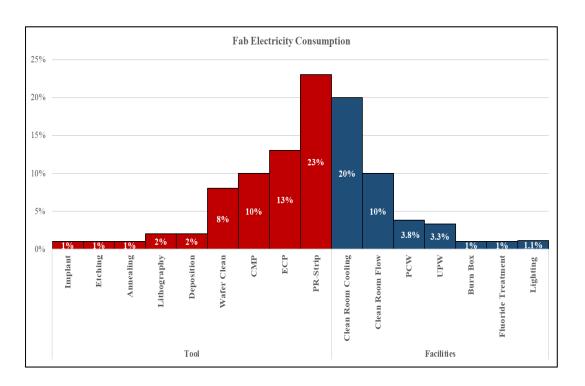

| 7.     | Fab Electricity Consumption                                           | .42  |

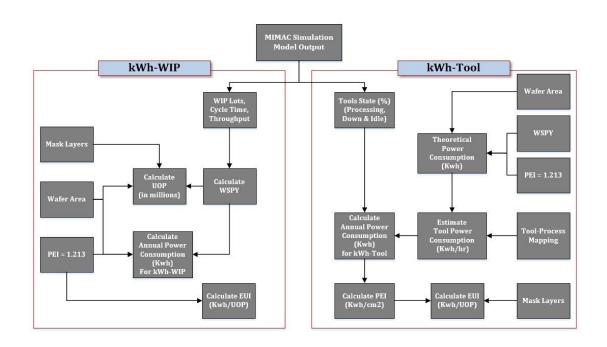

| 8.     | Simulation Process                                                    | .46  |

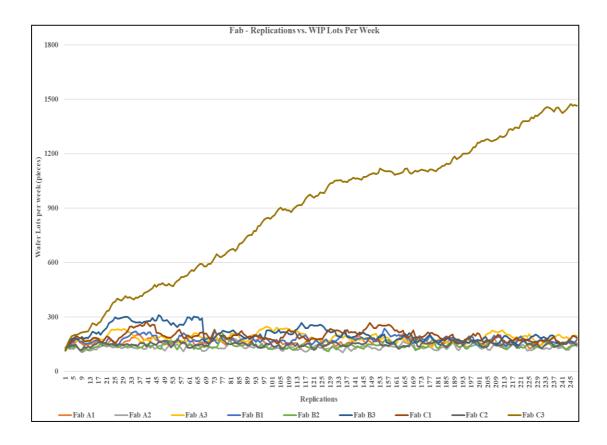

| 9.     | WIP lots recorded across scenario runs for every fab type             | . 50 |

| 10     | . Annual Power Consumption for kWh-WIP and kWh-Tool                   | . 57 |

| 11     | . kWh-WIP EUI vs. kWh-Tool EUI comparison                             | . 60 |

| 12     | . Bottleneck Station Utilization for each fab type                    | . 62 |

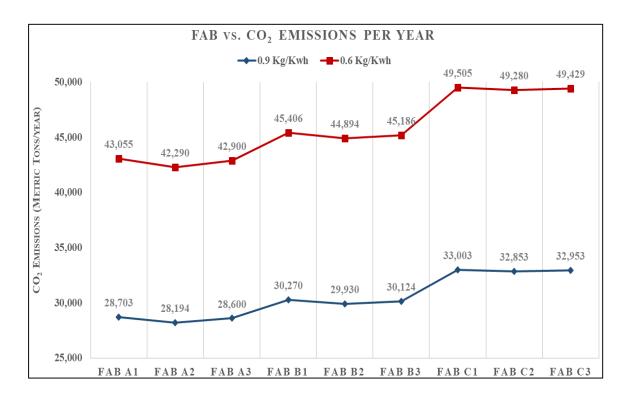

| 13     | . Carbon Emissions per year visualization for the different fab types | . 64 |

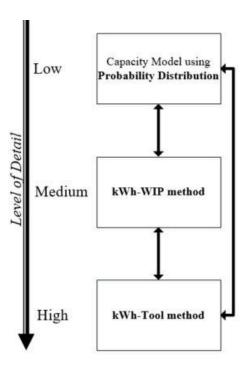

| 14     | . Methodologies and Anticipated Interactions in this study            | . 69 |

#### LIST OF ABBREVIATIONS

**Abbreviation Description**

IC Integrated Circuits

PC Personal Computer

WSTS World Semiconductor Trade Statistics

GHG Green House Gas

DG Distributed Generation

WT Wind Turbines

PV Solar Photovoltaic

OR Operation Research

WIP Work-in-Process

ITRS International Technology Roadmap for

Semiconductors

DRAM Dynamic Random-Access Memory

EUI Electrical Utilization Index

PEI Production Efficiency Index

UOP Units of Production

HVAC Heating, Ventilation, and Air Conditioning

EOQ Economic Order Quantity

PFC Perfluorocarbons

AMHS Automated Material Handling Systems

CT Cycle Time

TH Throughput

LP Linear Programming

BOM Bills of Materials

TI Texas Instruments

UPW Ultra-Pure Water

PCW Process Cooling Water

MEMS Micro-Electro-Mechanical Systems

RF chips Radio Frequency Chips

CMP Chemical Mechanical Polishing

ECP Electro Chemical Plating

WLSPY Wafer Lots Starts Per Year

WSPY Wafer Starts Per Year

MTTR Mean Time To Repair

MTBF Mean Time Before Failure

MIMAC Measurement and Improvement of Manufacturing

Capacity

DOE Design of Experiments

PFC Perfluorinated Carbon

RT Refrigeration Ton

#### **ABSTRACT**

Semiconductor industries are not only technology-intensive, but also highly energy-intensive. A wafer fab consumes about 300-400 kWh/day. To supply this amount of electricity, the amount of carbon dioxide released is approximately 180–360 metric tons per day. This emission causes climate change and also rise in energy costs. Thus, it is important to take measures to reduce energy consumption.

The scientific merit of this research is to develop two methods designed to estimate the electric energy consumption and production of a semiconductor wafer fab. The broader impact of the research is that the methods can be extended to other manufacturing industries, even though they are framed in this study in the context of the semiconductor manufacturing industry. The first method, referred to as kWh-WIP, is capacity model that estimates electricity consumption by using WIP lot information. The second method referred here as kWh-Tool is a capacity model that estimates electricity consumption by using tool-level utilization. A relation is established between the two levels of detail models by comparing them with respect to annual electricity consumption and carbon emissions. Power consumption of tools and tool-process mapping are obtained by intensive research and surveying with the professionals from the semiconductor manufacturing industry. The Measurement and Improvement of Manufacturing Capacity data set is used as the basis for the capacity simulations of this thesis work. The dataset represents 200mm wafer fab processes. The average Electrical Utilization Index (EUI) and Production Efficiency Index (PEI) computed with kWh-Tool methodology across all nine 200 mm fab considered in

this study was 0.145kWh/UOP and 1.987 kWh/cm<sup>2</sup> respectively. The average annual power consumption is 44,745,707 kWh. Annual Power Consumption values calculated in kWh-WIP and kWh-Tool methodologies are closer with a variation of less than 3%. The PEI values for different fab type computed from the kWh-Tool methodology is similar to the Optimal theoretical value of 1.231 (kWh/cm<sup>2</sup>).

#### 1. INTRODUCTION

## 1.1 Problem Description

Semiconductors are an essential part of many commonly used electronic devices, such as PCs, mobile phones, radios, tablets, and many more. Semiconductor manufacturing deals with producing integrated circuits (ICs) on silicon wafers, thin discs made from silicon and gallium arsenide. The semiconductor industry is a vast and highly competitive industry. The industry is characterized by large fluctuations in product supply and demand, depending heavily on the strength of the global economy. Worldwide semiconductor sales reached \$408.69 billion in 2017 according to the figures from World Semiconductor Trade Statistics (WSTS) [1].

Figure 1 Global Semiconductor Sales from 1987 to 2017 [1]

Figure 1 shows the global semiconductor industry sales each year. The Semiconductor Industry Association reports that the global semiconductor industry sales reached \$412 billion in 2017, which is an increase of 21.6% compared to the previous year. 2017 had the industry's highest-ever annual sales. Intel is the largest semiconductor chip manufacturer with revenues of 54 billion U.S. dollars in 2016 [1].

ICs are manufactured through a series of steps namely wafer fabrication, sort, assembly, and final test. The wafer fabrication part of the overall manufacturing process is carried out in semiconductor wafer fabrication facilities (wafer fabs). In this process, electronic circuits are built layer-by-layer onto the wafers – a process that might take a total processing time of several weeks depending on the product complexity. Wafer fabrication can be produced with in-house facilities or may be outsourced to subcontractors. Once they are processed in the wafer fab, wafers are sorted for any defects using electrical tests, after which the probed wafers are transferred to assembly facilities where dices of appropriate quality are packaged. These again are sent for testing to ensure that only high-quality products are delivered to the customers. Wafer fab and sorting are often referred to as the front-end, while assembly and test are called the back-end. All these processes utilize a large amount of electricity, particularly those done at the wafer fab.

A modern wafer fabrication facility consumes about 300-400 kWh/day on average, which can power approximately around 10,000 homes per day. Wafer fabrication processes are highly energy-intensive with annual energy utility bills of up to \$10–20 million for a single wafer fab [2]. To supply this amount of electricity, the amount of carbon dioxide released by fossil fuel-fired power plants is estimated to be 180–360 metric tons per day. This estimation is made based on the factor that 0.6–0.9 Kg CO<sub>2</sub> is released when 1 kWh

electricity is produced from a fossil fuel-fired power plant [3]. Climate change is a universally recognized 21st-century global environmental challenge. The impact of energy consumption on climate change and the rising cost of energy has become an extremely important issue faced by the semiconductor manufacturing industry today. Thus, chip manufacturers are increasingly driving efforts to reduce greenhouse gas emissions of their manufacturing facilities.

Energy efficiency has not been the high priority for management concern because energy costs were about 1-2 percent of total production costs, including buildings, capitalized land and equipment. This traditional way of viewing the fab's electricity consumption is now changing [2]. It is important to evaluate energy consumption in a semiconductor wafer fab because electricity is becoming one of the most expensive operational expenses. Energy costs can account for 5-30% of fab operating expenses, depending on the electricity prices. 30-40% percent of the fab's electricity consumption is from the wafer processing tools, whereas 50% of this consumption is due to the sub-fab systems, such as the air conditioning units, cleanroom heating, and ventilation [2].

Capacity planning involves determining the various facilities' resources required, with the focus in computing the number of tools that are required to maximize throughput (TH) with minimal work-in-process (WIP) and cycle time (CT). Jimenez et al. (2008) [4] reported several approaches for conducting capacity analysis for semiconductor manufacturing. These papers lack modeling components to enable the study of sustainability issues, such as carbon emissions and electricity consumption. Many papers with several mathematical models on environmental references and standards are available, but these models are unable to estimate electricity consumption. Estimation of energy

consumption is very important in order to reduce the CO<sub>2</sub> emissions by burning fossil fuels. This helps in reducing global warming. The cost of energy consumption can be reduced by incorporating renewable energy constraints into the capacity planning model. This also reduces the carbon dioxide emission and helps us to achieve sustainability. Renewable technology in the distributed generation system is quite appealing because they harness renewable sources for energy production, resulting in zero carbon emission.

# 1.2 Research Objective

This research proposes two capacity modeling methods to estimate electricity consumption and carbon dioxide emissions using key performance indicators, such as WIP, CT, and TH. The first method, called kWh-WIP, represents a capacity model for power consumption estimation using WIP lot data. The second method, called kWh-Tool, represents a capacity model for power consumption estimation using tool-level utilization data.

The research objectives are as follows:

- 1. To describe two simulation modeling methods that estimates annual electricity consumption and carbon dioxide emissions for a semiconductor wafer fab.

- 2. To compare the predictive accuracy of the simulation modeling methods performing under different scenarios varying the wafer starts per year and product mix levels.

- 3. To propose modeling guidelines and identify the obstacles of simulating the capacity model for predicting the fab's electricity consumption.

# 1.3 Thesis Outline

This thesis is organized as follows: Chapter 2 provides a detailed literature review based on previous work done in capacity modeling for production planning and capacity analysis in semiconductor manufacturing, with a focus on sustainability. Chapter 3 explains the methodology and describes the designed simulation model. Chapter 4 presents the designed simulation experiments and discusses the simulation results. Chapter 5 concludes this research and discusses future work.

#### 2. LITERATURE REVIEW

## 2.1 Semiconductor Manufacturing

Semiconductor manufacturing consists of front-end operations, where the surface of raw silicon wafers is modified to create a pattern of integrated circuits, and of back-end operations, where wafers are cut into individual microchips (dies), put in a package, and tested. It has become standard to term the fabrication and sort phases as the "front-end" and final test phases being called the "back-end."

**Figure** 2 Semiconductor Manufacturing [5]

The mass production of integrated circuits (ICs) can be divided into four different phases: fabrication, sort (probe), assembly, and final test [6]. Figure 2 displays an example of a semiconductor supply chain network. Fabrication is the process of transforming a pure silicon (or gallium arsenide) wafer into a wafer with completed ICs. This process requires 300 to 700 different process steps; this is the most complex portion of the entire process. The formation of one layer of the wafer can include cleaning, oxidation/diffusion, film deposition, photolithography, planarization, etching, ion implantation, and inspection; there may be up to 40 layers per wafer to build the completed ICs. Additionally, re-entrant flows exist, as the equipment used for these steps are expensive; the same wafer may be processed on the same machine multiple times (and competes for the machine's capacity with other wafers being produced) [7].

After a wafer completes fabrication, it proceeds to the sort (or probe) phase. The individual ICs on each wafer are tested for basic functionality. An electronic map is generated for each wafer, indicating those ICs on the wafer that failed. As in the fabrication phase, there is uncertainty in the number of ICs that survive sort. After sort is complete, wafers go to die bank (i.e., the completed wafer WIP) where they wait for the assembly and final test phases.

In the assembly phase, the wafer is cut into individual ICs or known as dies, and the failed ICs are discarded (scrapped). Functional ICs are then packaged wherein connections are made between the chip and the lead frame, and then the whole circuit is encapsulated for protection. The packaged ICs then move to the final test phase. At this point, the ICs are tested, rated (binned), and ultimately date-stamped for inclusion in finished goods inventory. These last two phases are still complex, but not to the extent of the first two; assembly and final test deal with millions of devices versus the thousands of wafers handled in fabrication and sort.

## 2.2 Electricity Consumption

Semiconductor manufacturing facilities, also known as wafer fabs, consume a large amount of electricity in daily operation as discussed above. The semiconductor manufacturing industry is confronted with two major facility challenges like many other industries, i.e., energy conservation and reduction of greenhouse gas emissions. ITRS has set aggressive goals for the industry about energy conservation in the next 10–20 years. More specifically, the wafer fab's energy consumption is expected to decrease from the current 1.9 kWh/cm² to 1.2 kWh/cm² by 2016 [8]. ITRS plans to achieve the goal by

implementing sustainable facilities and deploying green and cost-effective manufacturing processes.

Current approaches to sustainable manufacturing processes usually focus on energy conservation by improving equipment or tool efficiency. Although energy conservation is an effective method to improve the performance of wafer fabs, the following concerns are expressed by ITRS [2]:

- 1) The increase in the wafer size from 300 to 450 mm requires more energy per wafer;

- 2) The industry will potentially build new facilities or expand existing capacities to meet the market demand; and

- 3) The fabs carbon dioxide footprint from conventional power plants is difficult to quantify, and the criteria for controlling emission need to be defined.

Wafer fabs are highly energy-intensive and it consumes about 300–400 MWh per day [8], and 15-30 MW of daily load. This can power up to 10,000 homes in the U.S. In order to supply this amount of electricity, power plants are used but this emits 180–360 metric tons of carbon dioxide per day [3]. This value is calculated by assuming 0.6–0.9 Kg CO<sub>2</sub> released when 1 kWh electricity is produced [3]. A wafer fab typically contains hundreds of highly automated processing tools along with dozens of utility support systems, such as chillers, recirculating air fans, nitrogen plants, and exhaust air systems. The overall utility bill ranges from \$12-\$25 million. The three major factors dominating energy consumption in wafer fabs results are highlighted below [2]:

- 40% of energy is used to power the processing tools.

- 57% of energy powers the cleanrooms and recirculation air fans.

The remaining energy is used to supply ultra-pure water and pure gases to certain manufacturing processes.

Figure 3 Power Consumption of Semiconductor Fabrication Plant [2]

#### 2.3 Factors Affecting Energy Consumption in Wafer Fab

Hua et al. (2007) presented the factors affecting energy conservation in the wafer fab. Semiconductor wafer fab consumes a tremendous amount of electricity. Most fabs have cooling capacities over 10,000 RT (Refrigeration Tons), which is much larger than common commercial buildings. The energy allocation of the facility systems in a fab is affected by the following factors [9]:

- a. Fans consume high power to re-circulate filtered airflow in order to maintain a clean environment.

- b. Significant power is required to maintain stable cleanroom temperature and humidity (e.g.,  $24 \pm 0.5$  8°C and  $40 \pm 5$ %RH).

- c. Heat produced by the manufacturing process tools increases the load of the cooling system.

- d. Pumps and compressors consume significant electricity to produce ultra-pure water

(UPW) and gases.

- e. Treatment and processing of exhaust air require significant power. Energy is also used to pre-treat large volumes of outside air to compensate for the exhaust air in order to keep the cleanroom under positive pressure.

So, benchmarking is an important step in implementing energy conservation in a semiconductor fab. A semiconductor cleanroom facility system is complicated, usually comprised of several sub-systems, such as a chilled water system, a make-up system, an exhaust air system, a compressed air system, a process cooling water (PCW) system, a nitrogen system, a vacuum system, and an ultra-pure water (UPW) system. It is a daunting task to allocate energy consumption and determine an optimum benchmark.

Hu et al. (2010) researched on characterizing the energy use in 300mm DRAM (Dynamic Random-Access Memory) wafer fabrication plants in Taiwan by performing surveys and on-site measurements. The objective of this paper is to characterize the electric energy consumption and production of 300mm DRAM fabs by using various performance metrics. These performance metrics include the EUI (Electrical Utilization Index) and PEI (Production Efficiency Index). The results show that the EUI and PEI values are 0.0272 kWh/UOP and 0.743 kWh/cm², respectively. Using EUI in assessing the energy efficiency of the fab production provides more consistent comparisons than just using PEI [10].

Many of the actions undertaken to improve the energy efficiency of a manufacturing company are aimed at getting energy-consuming devices to operate more efficiently or at conserving energy within a plant. Such actions could include optimizing boiler efficiency, installing energy-efficient equipment, retrofitting fixed-speed motors with variable speed drives, or improving insulation in plant and buildings. While these device-oriented energy efficiency measures can achieve considerable savings, greater energy savings may be achieved in many instances by improving the efficiency of manufacturing processes.

The simplest and most valuable measure of energy efficiency achievements in a manufacturing plant is unit consumption or energy used per unit produced. Unit consumption provides the best indicator of how effectively the energy consumed by a plant is being used and can be tracked over time to measure energy efficiency improvements. If we define energy used per unit produced as a measure of energy efficiency in a manufacturing plant, then there are two complementary approaches to increase the energy efficiency of a plant: reducing energy consumption and increasing productivity. Factors

that reduce the productivity of a plant also reduce its energy efficiency. The greatest source of energy waste in any manufacturing plant could be an inefficient manufacturing process, a poorly planned production schedule, or poor product quality. An energy management policy that focuses only on improving the energy efficiency of energy-consuming devices or on energy conservation will not recognize or address these problems and will, therefore, have limited success. An effective energy management system should also incorporate energy-saving opportunities that can be realized by improving the overall production efficiency of a plant [11].

The cost of energy consumption can be reduced by incorporating renewable energy constraints into the capacity planning model. This also reduces the carbon dioxide emissions and helps us to achieve sustainability. Renewable technology like wind and solar generation system is quite appealing because they harness renewable sources for energy production, resulting in zero carbon emission.

#### 2.4 Simulation Models with Renewable Energy Integration

Long-term environmental sustainability can be achieved by incorporating renewable energy in the semiconductor wafer fab. Recently distributed generation (DG) emerged as a new system for energy production and consumption. DG units are installed in the consumer site where large electricity is needed. This technology is also an integral part of the smart grid with the goal of reducing the greenhouse gas emissions by adapting onsite renewable power generation. It includes wind turbines (WT), solar photovoltaics (PV), micro-turbines, diesel engines and fuel cells of which the capacity is usually less than 10 MW [3]. The advantages of using DG technology are:

- Since DG systems are installed on the site, it reduces the transmission bottleneck.

- There is no carbon emission.

- It refines the electricity supply reliability.

- Cost reduction in the utility bills.

Santana-Viera et al. (2015) proposed a distributed generation (DG) system comprising WT and solar PV units to power the wafer fab along with the main grid. The major challenge in deploying renewable DG technology is the power volatility. To design a robust DG system, both the power volatility and the load uncertainty must be appropriately quantified and incorporated into the design model. The purpose of the DG planning is to determine the generator type, capacity, and placement such that the overall system cost is minimized, or the energy yield is maximized [12].

The main obstacle to deploying wind and solar-based DG technologies is the high installation cost coupled with the intermittent power. Therefore, to reliably operate a renewable DG system, both the power intermittency and the payback period must be appropriately analyzed and incorporated into planning models. Several manufacturing and service industries have adopted onsite renewable energy to power their facilities along with the main grid. There is a lack of research activities targeting the modeling and implementation of wind–solar-based DG systems in a large manufacturing or public service settings.

Many papers leverage probability theories and analytics tools to model the random power generation and to optimize the capacity of onsite renewable DG systems. These papers, optimization models are formulated to determine the capacity of WT and PV units

such that the anticipated cost savings are maximized by considering the stochastic nature of wind speed and weather conditions.

A significant amount of electricity is required to support the operation of any large manufacturing facilities. Semiconductor manufacturing facilities, also known as wafer fabs, consume an enormous amount of electricity in daily operation. Integrating renewable energy into the wafer fabs alleviates the greenhouse gas emissions, reduces the utility bills and improves the energy security. A grid-connected DG system comprising of wind turbines, solar photovoltaics, a net metering module, and a substation is used. A quantitative approach is developed to guide the wafer fab to choose the energy technology and the generation capacity, aiming to minimize the system cost while mitigating the carbon footprint.

Villarreal et al. (2013) proposed the integration of renewable energy into the modern semiconductor industry. This paper presents a stochastic programming model to aid the planning and operation of distributed generation system in the presence of power volatility and load uncertainty. The proposed distributed generation (DG) system comprises WT and solar PV units to power the wafer fab along with the main grid [2].

Ziarnetzky et al. (2017) developed a model considering the elements of a sustainable and distributed generation system into a mid-term production planning formulation for a wafer fab. The major daily energy supply of the wafer fab is from the WTs and solar PVs. The surplus energy is returned to the main grid. Production-related costs, the cost for energy from the substation, and penalty costs when there is a lack of the renewable energy penetration were considered, and they could be reduced by offering renewable surplus energy to the main grid. A simulated environment was created to run

the obtained production plans to compute the expected profit in the face of machine breakdowns, wind power volatility, and uncertain power output of the solar PVs. This approach helps to determine an appropriate number of WTs and solar PVs for a given demand scenario. The results showed that it is reasonable to combine production-related planning and decisions with respect to the design of a DG system [6].

**Figure** 4 A Grid-Connected Solar PV and Wind Turbine System [5]

## 2.5 Carbon Emission and Carbon Tax

A carbon tax is defined as a fee imposed on greenhouse gas emissions generated by burning fuels. This tax puts a price on each ton of GHG emitted; this results in a powerful market response across the entire economy reducing emissions. These taxes can be a retrogressive tax; this may affect the low-income groups disproportionately directly or indirectly. Several countries have imposed carbon taxes or energy taxes. By increasing fuel efficiency, reducing fuel consumption, businesses and individuals, using cleaner fuels and adopting new technology can reduce the amount paid on the carbon tax [13].

In recent years, the global green tax landscape is evolving rapidly and becoming more complex, as governments widely use taxation as a tool to achieve green policy goals and make firms operate more sustainably. A number of pollution taxes are levied, and subsidies are offered around the world. In September 2012, the Japanese government introduced a new tax to curb greenhouse gas emissions [13]. France foisted a general tax for polluting activities names as "pay as you pollute." In the US, there are a large number of sub-national state-based tax incentives related to pollution control and ecosystem protection [13]. The carbon tax provides economic and social benefits. It aims to reduce the harmful and unfavorable emissions of CO<sub>2</sub> in the atmosphere, thus slowing down climate change and its negative effects on the human health and environment. It is a cost-effective method of reducing the GHG (Green House Gases) emissions.

Strand et al. (2015) analyzed the policy bloc of fossil fuel importers that prefers the tax to the cap. It executes an optimal climate policy, faces a fringe of other fuel importers and an exporter bloc. It purchases offset from the (non-policy) fringe. Since the tax reduces the price of fuel export and buys more when the policy bloc is larger, offsets are more favorable to the policy bloc under a tax when compared to the cap [14].

By taking into consideration the operational costs and social costs Hung et al. (2014) proposed a strategic decision-making model. These costs are caused by the CO<sub>2</sub> emission from a SCM for SSCM. Under different scenarios, the operational costs and carbon dioxide emissions were evaluated in the manufacturing SCM. The results showed that the amount of carbon dioxide emission came down with increasing social cost rate of carbon dioxide emissions. Lastly, it is concluded that the effective approach to reducing carbon dioxide emissions is to force the enterprises to bear the costs of carbon emissions resulting from their economic activities [15].

Jin et al. (2014) investigated on carbon emission tax, inflexible cap, and cap-and-

trade. Redesign of the supply chains and choices of transportation (truck, rail, or waterway) may influence a company. This paper mainly focuses on the optimization of the models for major retailers, who make a huge contribution to freight movement, to design their supply chains under various carbon policies. The policymakers can predict the impact of policies on overall emissions in the freight transportation sector using the results. The model, when incorporated into the integrated assessment models, can be effective in climate change analyses. Besides the impact of the policy parameters on carbon emissions and logistics cost is studied using a sensitivity analysis [16].

Du et al. (2009) emphasized on the influence of emission cap-and-trade mechanism in an emission-dependent supply chain. The emission dependent supply chain comprises of the emission permit supplier and the emission-dependent firm. Emission cap/quota imposed by the government and permits purchased via emission trading were taken into focus. Extra permits need to be purchased if the quota is inadequate to satisfy the target production. The unique Nash equilibrium derivation is presented, and a game-theoretical analytical model is proposed in this paper. Optimal decisions are made by the emission permit supplier on permit pricing and the emission-dependent firm on production quantity. The paper concludes that the governmental environment policy, several exogenous factors, the market risk, etc. affect the players' bargaining power [17].

Based on the economic order quantity (EOQ) model, Bian et al. (2015) examined the production lot sizing issues of a firm under two regulations, i.e., cap-and-trade and the carbon tax. This paper investigates the impacts of production and regulation parameters on the optimal lot size and emissions. It shows that under the cap-and-trade regulation, the firm's decision of the optimal emissions, as well as permits trading, depending on the

differentiated permits trading prices. The results show that, under the cap-and-trade regulation, the firm may buy some permits for production, or sell some surplus permits, or buy and sell no permits at all, depending on the value of the first cap [18].

Rapine et al. (2013) proposed a new model with environmental constraints, i.e., carbon emission constraints in multi-sourcing lot sizing problems. The constraints illustrated in this paper aims to reduce the carbon emission per unit of product supplied. A mode corresponds to the combination of a transportation mode and a production facility. It is characterized by its unitary carbon emission and economic costs. This paper suggested four types of constraints in the single-item capacitated lot sizing problem and required analysis is done [19].

Chi and Lan (2017) proposed four master planning models. These models include pollution taxes, progressive pollution taxes, and subsidies into capacity allocation to evaluate the problem of anthropogenic PFC (Perfluorinated Carbon) emissions. Reducing global warming is the need of the hour with the continued development of manufacturing industries along with increasing greenhouse gas emissions. For a successful environmental plan to be implemented, subsidies and/or progressive taxes for foundry plant should be introduced. The first step in this process is to set emission limits and also to consider master planning taxation [20].

Song et al. (2016) studied the emission-dependent firms in the cap-and-trade system and worked on the effects of carbon footprint and low-carbon preference on the production decision. The total "cap" is used to attain environmental goals that allow the "trade" to achieve effective scheduling through market regulation. By analyzing the impact of the carbon footprint and low carbon need in the market supply and demand a production

optimization model is designed [21].

Benjaafar et al. (2013) proposed carbon incorporation into the operational model. The authors emphasized the impact of operational decisions on carbon emissions and the degree to which adjustments to operations can alleviate emissions. The results showed that operational changes lead to significant emission control, and thereby, there was no increase in the cost. The results also highlight an option of reducing the cost of emissions to leverage collaboration across the supply chain [22].

Du et al. (2015) proposed a carbon emission dependent supply chain model. The requisite for production is an emission-dependent supply chain comprising of one single emission permit supplier and one single emission manufacturer in the cap-and-trade system, where emission permit becomes essential for production. Government allocates the emission cap of the emission-dependent manufacturer as a kind of environmental policy and investigates its influence on decision-making within the concerned emission-dependent supply chain. It also considers the distribution fairness in social welfare. It proves that the manufacturer's profit increases with the emission cap. In certain conditions, there is an option for the manufacturer and permit the supplier to coordinate the supply chain to get more profit [23].

A two-stage game theory model to analyze the impact of carbon tariff and tax was put forth by Tian et al. (2015). This article focuses on the optimal carbon tax policy imposed by countries and the impact of this policy on firms' optimal production decisions. This article presented a different perspective in investigating the effect of the carbon tax and tariff. The study considers two consuming markets and the strategic game between the two countries. The results show that the environmental damage level significantly affects

the demand in an unstable market [24].

He et al. (2016) studied the joint production and pricing problem in a semiconductor manufacturing firm with cap-and-trade and carbon tax regulations on multiple products. The effects of the two regulations are compared to the total carbon emissions, social welfare, and the firm's profit. The demands for these products are independent, and the firm faces a price-sensitive demand. Firstly, the optimal number of products to be produced under cap-and-trade regulation (carbon tax regulation) is determined by the emission trading prices along with the cap (tax rate). Secondly, the optimal cap (tax rate) is decreasing (increasing) or constant in the environmental damage coefficient is found. Finally, it is discovered that social welfare subjected to carbon tax regulation is not less than that subjected to cap-and-trade regulation. Even though there is neither one regulation always producing more profit and having advantages in suppressing carbon emissions than the other one [25].

Wang and Liang (2015) performed a study that aims to assess the impacts of taxing carbon on China's primary income distribution from an economy-wide perspective. The results show that carbon taxing would reduce labor remuneration and its share of the primary distribution and capital income and increase the net product tax and its share. This result indicates that taxing carbon will benefit the government but deteriorates China's primary income distribution status, and damage both households and enterprises. The carbon tax would perform differently under different labor scenarios and different critical elastic values. This paper concludes that during the transition period the complex features of China's labor market and the development of production technology should be taken into consideration when introducing a carbon tax [26].

#### 2.6 Production Planning of the Supply Chain Model

The purpose of production planning is to match the output of production facilities to external demand in a manner that optimizes some performance measure for the firm. The production planning decision is the quantity and the timing of material released into the plant so that output emerges to meet the customer's demand in a timely fashion. This requires knowledge of the time elapsing between the releases of work into the plant cycle, the time of the production process and its emergence as a finished product that can be used to meet demand. However, queuing models have shown that average cycle times depend on resource utilization, which is determined by the release decisions made by the planning models.

Uzsoy et al. (1992) published a paper describing the characteristics of semiconductor manufacturing environments and reviewed research on system performance evaluation and production planning. They focused on the characteristics of the semiconductor manufacturing process that make production planning and scheduling difficult. The production planning and system performance evaluation were studied. The paper classifies the research by the solution technique used and further analyses its advantages and disadvantages [27].

Karabuk et al. (1999) focused on the strategic capacity planning problem by considering operational planning decisions as the short-term recourse of the capacity plan. This study is performed at a major US semiconductor manufacturer company on real planning scenarios. The main property of the semiconductor capacity planning is that the product demands, and manufacturing capacity is uncertain. The high demand microelectronic chip will become outdated with the invention of the next-generation chip;

this requires an improved manufacturing process. This can create high variability in the outcomes and causes uncertainty in the throughput and in the capacity estimations. This paper concluded that different scenarios should be considered during long-term capacity planning [28].

To meet supply to demand in an ideal manner, the cycle time that elapses between the material being introduced into the plant and its emergence as a finished product should be recognized. Production planning models that aim at determining optimal release schedules for production facilities face a fundamental circularity.

Toktay et al. (1994) addressed the capacity allocation problem in a semiconductor wafer fabrication facility emerging as a subproblem of an artificial intelligence-based scheduling system. Differences in machine capabilities, setup considerations, and tooling constraints are considered. The example analyzed in this paper has seven repeated lithography and etching processes, and four diffusion times. The main objective of this paper is to focus on minimizing deviation and maximizing throughput from the predetermined production goals. The problem formulations are concluded as a maximum flow problem on a bipartite network with integer side constraints and to develop efficient heuristics to obtain optimal solutions in very less computation time [29].

Swaminathan (2000) described a model under uncertainty in demand for the tool capacity planning problem. Technology and products are changing rapidly, combined with long procurement lead times for tools made it extremely difficult to procure tools efficiently. The paper provides two heuristics analysis to overcome this problem; one based on the tool cost data and the other based on a greedy approach to procuring tools. This heuristic analysis is used to find an efficient tool procurement plan and test their quality by

using lower bounds on the formulation [30].

Liu et al. (2011) presented a complete framework for strategic capacity expansion of semiconductor manufacturing production equipment. This approach is applied to the wafer fabrication facility model. It integrates computer simulation, queue analysis and adaptive statistical methods to generate many good reconfiguration alternatives. The outcome of this method presented is a number of good system configurations. The overall performance and each configuration are distinguished by their Cycle time CT-Throughput TH profiles. The CT-TH profiles define the complete performance of the system at different demand scenarios. This study can be used in capacity expansion decisions to evaluate the alternative configurations [31].

Stray et al. (2006) developed a model for global logistics and resource optimization in a semiconductor manufacturing operation. It aimed at resource allocation and strategic decisions for long-term planning in the industry. Various parameters, such as product manufacturing area, the opening of new facilities, adding new tools, and subcontract, were decided. This paper discusses the problem i.e., the allocation of products to wafer fabrication facilities and routing the wafers with the integrated circuits for testing. The processed wafers are cut into individual chips and put in a package. A package is a frame that is designed to protect the chip and provide a connection between the chip and the excess testing and classification which are later routed to the final test facilities. This paper demonstrated a mixed-integer programming (MIP) model that maximizes sales revenue subtracting the production, transportation, and acquisition costs of a semiconductor manufacturing firm subjected to demand and capacity constraints. Decision variables include what to produce, where to produce, production quantity, what facilities should be

built/closed, and what equipment should be purchased/sold [32].

Catay et al. (2006) studied the strategic level investment decisions for obtaining an overall level of capacity planning and new equipment. The problem of wafer production planning within a single facility over multiple time periods is observed. This problem is addressed by using the multi-period MIP model. The demand forecast values of each wafer type for each period are known. This model minimizes the machine tool operating costs, inventory holding costs, and new tool acquisition costs. Lagrangian based relaxation heuristic is used to find the effective plans for procuring tools [33].

Mönch and Ziarnetzky (2016) presented a production planning formulation in a simplified semiconductor supply chain based on clearing functions. The semiconductor supply chain comprises of a single front-end and back-end facility. The objective function described in this paper is based on cost. The parameter of this model is the minimum utilization of expensive bottleneck machines in the front-end facility, the less expensive capacity of the back-end facility can be increased to reduce the cycle time in the backend facility. The release schedules obtained from the planning formulations are evaluated using discrete-event simulation. To determine proper capacity expansion levels for the back end and appropriate minimum utilization levels for the front-end bottleneck machines. The results of the experiments indicate that the profit can be increased by maintaining the maximum possible cycle time [34].

#### 2.7 Modeling Sustainability for Production Planning

Production planning with the consideration of environmental cost impacts has become a growing segment of the overall effort to gain competitive excellence in the market. There is an increasing awareness of the environmental costs, such as pollution

charges and resource conservation fees, which must be considered in the production planning scheme in an uncertain environment. Many production planning and control may not be able to address the upcoming issues of potential costs for pollution charges and resource conservation fees.

The concept of sustainable development supposes the realization of the objectives connected to the economic growth and the environment. Reiborn et al. (1999) proposed that in the long run, the investments in the systems for environmental management are less than the benefits of the firms. The importance of the problems connected with environmental protection and pollution prevention is a stimulus for research in mathematical modeling of production processes [35].

Rădulescu et al. (2009) formulated several optimal production planning models considering various environmental constraints. This paper presented two stochastic programming problems, a maximum expected return problem, and a minimum pollution risk problem. This paper formulated a multi-objective programming approach with suitable constraints on pollutant emissions for production processes. Each model had two optimization problems, namely, minimum pollution risk and maximum expected return. This model is investigated by considering various cases of contamination levels, i.e., desired, critical and acceptable levels of textile plant emissions [36].

Environmental issues play an essential role in the normal activities of business firms. Decisions on production planning, allocation, location, logistics and inventory control will change due to consumer pressures or legal requirements to reduce waste and emissions. Therefore, there is a need to adopt OR tools such as production planning algorithms, location models and routing heuristics to deal adequately with a new situation

requiring 'green supply chain modeling.' The production-distribution-consumption process is a source of well-known Operational Research applications such as network optimization and routing, production planning and scheduling, inventory control, etc. These applications can be examined to see how environmental issues can be effectively integrated and how this integration influences model structure and solution methods. Pirila et al. (1994) studied emission-oriented production planning in the Finnish pulp and paper industry. Their production planning model is a large multiple-period linear programming. Integration of environmental impacts within this model leads to alternative strategies, including process choices, recovery of waste products, etc. [37]. Haasis (1994) studied production planning and control of less emitting production systems. The methodologies used are based on dynamic programming, priority-based heuristics and neural networks (machine learning) [38].

Golari et al. (2017) presented a multi-period, production-inventory planning model in a multi-plant manufacturing system powered with onsite and grid renewable energy. The model is to determine the stock level, the production quantity, and the renewable energy supply in each period such that the production cost (including energy) is minimized. Three steps are used to tackle decision problems. First, a deterministic planning model to attain the desired green energy penetration level is presented. Next, the deterministic model is extended to a multistage stochastic optimization model considering the uncertainties of renewables. Finally, an efficient modified Benders decomposition algorithm is developed to search for the optimal production schedule. Numerical experiments are presented to validate and verify the model integrity. The paper also discusses and justifies the potential of realizing high-level renewables penetration in large manufacturing system [39].

Chaabane and Geramianfar's (2015) multi-objective decision-making framework for sustainable supply chain optimization network consists of production plants, distribution centers and retailers (customers). A multi-product and multi-period planning model are described, and the sustainability was evaluated based on three performances: cost, GHG emissions, and service level. This model was tested on a Frozen Food industry. Preliminary results showed that the three objectives are conflicting. They proposed that just in time distribution might increase total cost but reduce GHG emissions due to the best control of inventories at distribution centers and retailers. The decision-making model helps to identify the trade-off between the three conflicting objectives and take the best decisions to achieve sustainability objectives of the supply chain [40].

Zhang and Xu (2013) researched on multi-item production planning problem with carbon cap and trade mechanism where a firm uses a standard capacity and carbon emission quota to produce multiple products. This analysis satisfies the stochastic independent demands, and on a trading market of carbon emission, the firm can buy or sell the right for carbon emissions. A profit-maximization model that analyses the carbon trading decisions and policy of production is designed. This paper presents an efficient solution with linear computational complexity for solving the optimal solution [41].

Helmrich et al. (2015) considered a generalization of the lot-sizing problem with the emission capacity constraint. There are emissions associated with production, setting up the production process and keeping inventory. This paper describes that NP-hard is lot-sizing with an emission capacity constraint. The algorithm mentioned in this journal can handle a fixed-plus-linear cost structure, more general concave cost, and emission functions. Initially, a Lagrangian heuristic is demonstrated to provide a feasible solution

and the lower bound for the problem. A pseudo-polynomial algorithm is presented to fulfill the costs and emissions. This analysis can also be used to identify the complete set of Pareto optimal solutions of the bi-objective lot-sizing problem [42].

Ziarnetzky et al. (2017) developed a model considering the elements of a sustainable and distributed generation system into a mid-term production planning formulation for a wafer fab. The generation system included the Wind turbines (WTs), solar photovoltaics (PVs), a substation with grid access, and a net metering system. The major daily energy supply of the wafer fab is from the WTs and solar PVs. Surplus energy is then returned to the main grid. Production-related costs, the cost for energy from the substation, and penalty costs when there is a lack of the renewable energy penetration were considered, and they could be reduced by offering renewable surplus energy to the main grid. A simulated environment was created to run the obtained production plans to compute the expected profit in the face of machine breakdowns, wind power volatility, and uncertain power output of the solar PVs. This approach helps to determine an appropriate number of WTs and solar PVs for a given demand scenario. The results showed that it is reasonable to combine production-related decisions and decisions for the design of a DG system [6].

From the above literature review, the increased market requirement has resulted in the increase of total energy consumption for the semiconductor wafer fab. The energy use required for operating semiconductor wafer fab and their processes is very high. This is also one of the major concerns to production power reliability, cost-cutting efforts, and to reduce the environmental impact. It is important to develop optimization model on energy use and assess energy saving potentials in a long run. In the next chapter, different methods are presented to calculate the energy consumption in a semiconductor wafer fab by

considering various performance metrics. This energy consumption allows us to calculate the total amount of carbon dioxide released into the air. MIMAC model is used for the simulation.

#### 3. METHODOLOGY

This chapter presents two modeling methods to characterize a wafer fab's electrical energy consumption using various performance metrics produced by the traditional capacity simulation model. The first modeling method, an abstract modeling approach called the kWh-WIP, estimates the electricity consumption using throughput, cycle time, work-in-process and production efficiency index. The second modeling method, a more detailed modeling approach called the kWh-Tool, estimates the electricity consumption using tool utilization.

The MIMAC data set is used as the basis for the capacity simulations of this thesis work. The dataset represents 200mm wafer fab processes. The increase in demand for analog, RF chips and MEMS causes a shortage for the capacity and equipment in 200mm fab. This situation raises the need for energy efficiency and capacity planning for the 200mm fabs to meet their demand. The MIMAC simulation model and the methodologies to analyze the energy consumption and performance metrics for both levels of details are discussed in detail in this chapter.

# 3.1 List of Variables and Parameters

# • Variables:

| Variables                              | Description                                                 | Units               |

|----------------------------------------|-------------------------------------------------------------|---------------------|

| TH                                     | Average wafer starts per year or demand of the fab          | pieces              |

| WIP                                    | Average WIP lots at the end of period T                     | lots                |

| ĈT                                     | Average Cycle Time during period T                          | minutes             |

| ÛÔP                                    | Average Units of Production                                 | millions            |

| Ĺ                                      | Annual Electricity Consumption of the fab                   | kWh                 |

| PÊI                                    | Computed PEI from simulation results                        | kWh/cm <sup>2</sup> |

| ÉÛI                                    | Computed EUI from simulation results                        | kWh/UOP             |

| $\widehat{e_{up,i}}$                   | Electricity Consumption of Tool i at Up State in period T   | kWh                 |

| $\widehat{e_{down,i}}$                 | Electricity Consumption of Tool i at Down State in period T | kWh                 |

| $\widehat{e_{idle,i}}$                 | Electricity Consumption of Tool i at Idle State in period T | kWh                 |

| $\widehat{S_{\mathrm{up,i}}}$          | Average Up percent for tool $i$ in period T                 | %                   |

| $\widehat{S_{\text{down,1}}}$          | Average Down percent for tool $i$ in period T               | %                   |

| $\widehat{S_{idle,i}}$                 | Average Idle percent for tool $i$ in period T               | %                   |

| $\widehat{\mathrm{L_{up}}}$            | Total Power Consumption during Up time                      | kWh                 |

| $\widehat{\mathrm{L}_{\mathrm{down}}}$ | Total Power Consumption during Down time                    | kWh                 |

| $\widehat{\mathrm{L}_{Idle}}$          | Total Power Consumption during Idle time                    | kWh                 |

| FCE                                    | Annual Fab Carbon Emissions                                 | MTons/year          |

# • Parameters:

| <b>Parameters</b> | Description                       | Value      | Units               |

|-------------------|-----------------------------------|------------|---------------------|

| A                 | Wafer Area                        | 314.22     | $cm^2$              |

| M                 | Wafer Mask Layers                 | 8.5 - 10   | nos.                |

| PEI               | Theoretical PEI                   | 1.312      | kWh/cm <sup>2</sup> |

| WLSPY             | Wafer Lot Starts per year         | Lots * 52  | lots                |

| WSPY or TH        | Wafer Starts per year             | WSPLY * 48 | pieces              |

| T                 | Length of Simulation Run          | 8,760      | hours               |

| $CO_2$            | Range of Carbon Dioxide Emissions | 0.6 -0.9   | kg/kWh              |

## **3.2 Capacity Performance Measures**

# • Cycle Time (CT):

Cycle time can be defined as the average time from release of the job at the beginning of the routing until it reaches an inventory point at the end of the routing or time that part spends as a work in progress [31]. It can also be defined as the time taken to complete the production of one unit from the beginning to end.

# • Throughput (TH):

For a production line, throughput is defined as the average quantity of good parts produced per unit time [31].

#### Work-in-Process (WIP):

Work-in-Process is defined as the inventory between the start and end points of a product routing. It can be used as one parameter to calculate and measure efficiency [31].

#### • Little's Law:

Little's law describes the essential relationships among WIP, CT, and TH. The power of Little's law lies in its ability to influence team behavior with its underlying constraints [31]. It helps the user to use a given scale to benchmark actual production systems. For instance, to increase the throughput of a production line limit the WIP in the system or speed up the process to once again limit the WIP. The fundamental relationship between WIP, CT, and TH over the long-term is:

$$WIP = TH \times CT \tag{1}$$

#### • Units of Production (in millions):

The units of production (UOP) of a fab are defined as:

$$UOP = TH \times A \times M \tag{2}$$

The number of mask layers is used to represent the complexity of production. Number of masks is directly proportional to the number of processes required to produce a wafer. Considering the throughput or wafer starts (TH), wafer surface area (A), and an average number of mask layers (M), Units of Production (UOP) gives a good estimate of the total production capability of a wafer fab [45].

# **3.3 Electricity Consumption Metrics**

The characterization of power consumption of a wafer fab is defined by the following performance metrics.

- 1. Production Efficiency Index (PEI)

- 2. Electrical Utilization Index (EUI)

The performance metrics can also be used to track the efficiency trends associated with products that are evolving. These efficiency indicators are largely defined using normalization methods, i.e., dividing electric power consumption of the wafer plants or tools by a unit measuring the scales of wafer production (e.g., number of units or wafer area).

#### Production Efficiency Index:

Production Efficiency Index (PEI with a unit of  $kWh/cm^2$ ) is defined as a fab's total annual electricity consumption divided by its total wafer surface area produced. It represents the energy efficiency of a fab without including the complexity of the wafer production, but the physical scales of wafer area are processed.

$$PEI = \frac{L}{TH \times A}$$

(3)

#### • Electrical Utilization Index:

Electrical Utilization Index (EUI with a unit of *kWh/UOP*) is defined as a fab's total annual electric power consumption divided by its annual UOP. EUI quantifies the energy efficiency of how a fab uses electric power consumption for wafer production, which considers the wafer process complexity.

$$EUI = \frac{L}{UOP} \tag{4}$$

### 3.4 Comparison of PEI and EUI

PEI and EUI are defined to quantify and compare the energy efficiency of the fabs. The efficiency trends associated with products evolving over time can be tracked by using the above-mentioned performance metrics. These performance indicators are normalized based on dividing electric power consumption of the wafer plants or tools by the number of units or wafer area. Notably, PEI is similar to EUI except that the number of mask layers is not considered. The mask layers define the complexity of the processes. The number of mask layers is proportional to the number of processes required to produce a wafer. Therefore, PEI index does not represent the complexity of the product, only the quantity of wafer area [45].

# 3.5 Capacity Model for Electrical Power Consumption Estimation using WIP Lot Data (kWh-WIP)

The model presented by formulas in Equations (1) -(7) calculates power consumption by using WIP-lot data, UOP and PEI values.

#### • kWh-WIP Model:

$$\widehat{\text{UOP}} = \frac{\widehat{\text{WIP}}}{\widehat{\text{CT}}} \times A \times M \tag{5}$$

$$\widehat{L} (kWh) = PEI \times \widehat{TH} \times A$$

(6)

$$\widehat{L}(MW) = \frac{\widehat{L}(kWh)}{T}$$

(7)

where T is the number of hours in the simulation run.

In Equation (5),  $\widehat{\text{WIP}}$  represents the average number of lots that are being processed during a simulation run. This is a critical input for energy consumption calculations. Using Little's Law in Equation (1), average cycle time gives average throughput. Therefore, the units of production for this particular fab model is computed based on the wafer area and the number of mask layers in this process. With electric energy consumption guidelines for WIP and the selected optimal PEI value, the computed throughput  $\widehat{TH}$ , and wafer area energy consumption of the fab is calculated. The total annual power consumption of the fab  $\widehat{L}$  (kWh) is computed from equation (6). Equation (7) represents the load of the fab in MW. This value is obtained from computed load  $\widehat{L}$  (kWh) divided by the simulation period

in hours. Furthermore, other performance parameters like EUI is computed with the theoretical PEI and wafer mask layers (M).

# 3.6 Capacity Model for Electrical Power Consumption Estimation using Tool-level Utilization (kWh-Tool)

This method in Equations (8) -(13) estimates the energy consumption of a wafer fab by analyzing the energy utilization of each station-process.

### kWh-Tool Model:

$$\widehat{\mathbf{L}_{\mathrm{up}}} = \sum_{T} \sum_{i}^{72} \widehat{\mathbf{e}_{\mathrm{up,1}}} \times \widehat{\mathbf{S}_{\mathrm{up,1}}}$$

(8)

$$\widehat{\mathbf{L}_{\text{idle}}} = \sum_{T} \sum_{i}^{72} \widehat{\mathbf{e}_{\text{idle,i}}} \times \widehat{\mathbf{S}_{\text{idle,i}}}$$

$$(9)$$

$$\widehat{L_{\text{down}}} = \sum_{T} \sum_{i}^{72} \widehat{e_{\text{down,1}}} \times \widehat{S_{\text{down,1}}}$$

(10)

$$\widehat{L} = \widehat{L_{up}} + \widehat{L_{down}} + \widehat{L_{idle}}$$

(11)

Where  $\hat{L}$  is the annual power consumption of the fab

$$\widehat{PEI} = \frac{\widehat{L}}{TH \times M}$$

(12)

Where TH is the throughput or the wafer starts per year of the fab.

$$\widehat{EUI} = \frac{\widehat{PEI}}{M} \tag{13}$$

where M is the wafer mask layers.

This project considers three states:

- <u>Idle State</u>: The percent of the time when the station is available and awaiting a process to start.

- <u>Down State</u>: The percent of the time when the station is unavailable for processing or requires repair or maintenance.

- <u>Uptime State</u>: The percent of the time spent in processing and sum of all the other states except idle and down.

This research assumes that these states do not consume an equal amount of power. In other words, each station consumes different percent of power at different states, highest being processing. As per our analysis, the Uptime State consumes 100%, Idle State consumes 90%, and Down State consumes 75% of the station energy allocation [43] [44].

After running the simulation model for a definite period, the average state (Down, Idle, and Up) % values are recorded over period T. With equations (8), (9) and (10), the recorded average states (%) for a tool 'i' is multiplied with the power consumption allocation of tool 'i' for that particular state.  $e_{\widehat{up},l}$ ,  $e_{\widehat{down},l}$ , and  $e_{\widehat{idle},l}$  are the energy consumption of tool 'i' at states up, down and idle respectively.  $\widehat{L_{up}}$ ,  $\widehat{L_{down}}$ , and  $\widehat{L_{ldle}}$  is the sum of energy consumption for all tools in up, down and idle states respectively.

Equation (11) represents the overall power consumption calculation, with  $\hat{L}$  denoting the overall fab load per year and corresponding load for different tool states. Equation (12) defines the Performance Efficiency Index ( $\hat{PEI}$ ) calculation for kWh-Tool

methodology. In this equation, 'TH' is the capacity or defined as wafer starts per year of the fab, and 'M' is wafer masks layers. With the annual power consumption of the fab and the wafer area with demand, the PEI metric is computed. Further, Electrical Utilization Index EUI is defined in equation (13), with (PEI) divided by the number of mask layers. The goal is to show the relationship between theoretical PEI and computed PEI; to validate the kWh-Tool methodology.

# 3.7 Carbon Dioxide Emission Calculation

In order to supply the calculated amount of electricity, the amount of carbon dioxide released by fossil fuel-fired power plants, etc. is estimated to be 180–360 metric tons per day. This estimation is made based on the factor that 0.6–0.9 Kg is released when 1 kWh electricity is produced from a fossil fuel-fired power plant [2]. Assuming the carbon emission to be 0.6-0.9 kg for 1 kWh of electric energy, equation (14) calculates the annual carbon emission is calculated for every fab type expressed in terms of metric tons per year.

$$FCE\left(\frac{metric\ tons}{year}\right) = CO_2 \times \hat{L}$$

(14)

Where, FCE is the amount of carbon emissions recorded by the fab in a year (in metric tons per year) and

$CO_2$  emission range vs. power consumption is set between = 0.6 - 0.9 Kg/kWh

#### 3.8 Description of Simulation Model

The MIMAC was a joint project of JESSI/MST and SEMATECH to identify and measure the effects and interactions of major factors that cause a loss in fab efficiency (Fowler and Robinson, 1995) [46]. This research uses the MIMAC reference model to

analyze the electricity utilization in a 200mm semiconductor wafer fab. Inputs and outputs for the model are shown in Figure 5.

Figure 5 Inputs and Outputs for the MIMAC Model

Nine different fab scenarios are identified based on wafer starts per year and product mixes with the MIMAC dataset. The demand for the fab is represented by wafer starts per year. The product mixes correspond to the ratio of production between Part A vs. Part B. The technology usage and MIMAC simulation model set up is discussed in section 3.10.

The MIMAC dataset comprises 71 station families and 220 stations. These station families include Lithography, Annealing, ECP, CMP, Etching, Deposition, Photo-resist strip, wafer clean and implant. Table 1 summarizes the station family to process mapping. Figure 6 depicts the number of stations per station family.

Table 1 Station Family –Process Mapping

| 1. Implant                       | 2. Deposition                    | 3. Etching                        |

|----------------------------------|----------------------------------|-----------------------------------|

| • GENUS                          | BPSG                             | • AME_8310                        |

| HIGH_CURREN                      | <ul> <li>DELAMINATOR</li> </ul>  | • AME_8330                        |

| T_IMP                            | <ul> <li>LAMINATOR</li> </ul>    | • E_SINK                          |

| <ul> <li>IMPLANT_OX</li> </ul>   | • LTO                            | • MATRIX                          |

| <ul> <li>MED_CURRENT</li> </ul>  | OXIDE 1                          | OXIDE_LAM                         |

| _IMP                             | SILICIDE_TOOL                    | POLY_LAM                          |

| <ul> <li>POLY_DOPE</li> </ul>    | _                                | • RAINBOW_4500                    |

| <ul> <li>VARIAN</li> </ul>       |                                  | _                                 |

| 4. ECP                           | 5. Wafer Clean                   | 6. Lithography                    |

| <ul> <li>ANELVA</li> </ul>       | <ul> <li>DIFF_SINK1</li> </ul>   | <ul> <li>ALIGNER</li> </ul>       |

| <ul> <li>BARRIER_OX</li> </ul>   | DIFF_SINK2                       | CRIT_COAT                         |

| CD_MACH                          | • DIFF_SINK3                     | CRIT_DEV                          |

| <ul> <li>DRIVE_OX</li> </ul>     | • DIFF_SINK4                     | NONCRIT_COAT                      |

| FIELD_OX                         | DIFF_SINK5                       |                                   |

| <ul> <li>FINAL_VISUAL</li> </ul> | <ul> <li>DIFF_SINK6</li> </ul>   | <del>-</del>                      |

| • GATE                           | <ul> <li>DIFF_SINK7</li> </ul>   | SECOND_MASK                       |

| <ul> <li>INTERGATE</li> </ul>    | DIFF_SINK8                       | • STEPPER                         |

| <ul> <li>LASER_SCRIBE</li> </ul> | • FSI                            | <ul> <li>VAPOR_PRIME_O</li> </ul> |

| LEITZ_ETCH                       | <ul> <li>METAL_SINK</li> </ul>   | VEN                               |

| <ul> <li>LEITZ_LITHO</li> </ul>  | • SINK_22_BOE                    | NEW_STEPPER                       |

| <ul> <li>NANOSPEC</li> </ul>     | • SINK_22_CAROS                  |                                   |

| <ul> <li>NITRIDE</li> </ul>      | • SINK_24_BOE                    |                                   |

| • PEAK                           | • SINK_24_CAROS                  |                                   |

| <ul> <li>POLY_DEP</li> </ul>     | ULTRASONIC_C                     |                                   |

| <ul> <li>PROMETRIX</li> </ul>    | LEAN                             |                                   |

| <ul> <li>QUAESTAR</li> </ul>     | <ul> <li>ULTRASONIC_T</li> </ul> |                                   |

|                                  | OOL                              |                                   |